# Protean: A Programmable Spectre Defense

Nicholas Mosier

*Department of Computer Science

Stanford University

Stanford, USA

nmosier@stanford.edu*

John C. Mitchell

*Department of Computer Science

Stanford University

Stanford, USA

jcm@stanford.edu*

Hamed Nemat

*School of Electrical Engineering and Computer Science

KTH Royal Institute of Technology

Stockholm, Sweden

hnnemati@kth.se*

Caroline Trippel

*Departments of Computer Science and Electrical Engineering

Stanford University

Stanford, USA

trippel@stanford.edu*

**Abstract**—We present the PROTEAN Spectre defense—the first to be altogether *comprehensive*, covering all side-channels and speculation; *programmer-transparent*, requiring no source modifications; and *programmable*, tailoring its hardware protections to software’s security needs. Several Spectre defenses offer the first two features, but protect a hardware-defined subset of architectural state from transiently leaking. Meanwhile, many Spectre-vulnerable programs process secrets in ways that such rigid protections cannot both performantly and fully secure. PROTEAN overcomes this limitation through: (1) ProtISA, an ISA extension that allows software to tell hardware which architectural registers and memory bytes require protection from transiently leaking at each program point; (2) ProtCC, a compiler that automatically infers and programs ProtISA protections for vulnerable code with minimal user input; and (3) ProtDelay and ProtTrack, two alternative hardware mechanisms that performantly enforce software-defined ProtISA protections. By flexibly tailoring a hardware Spectre defense to a program’s data protection needs, PROTEAN significantly reduces the overhead of fully securing vulnerable programs. With ProtDelay/ProtTrack, it averages  $0.27x/0.18x$  and  $0.42x/0.34x$  of the runtime overhead of the best secure baseline for programs with and without mixed security needs, respectively, at lower/comparable hardware complexity.

**Index Terms**—Hardware security, hardware side-channel attacks, Spectre defenses, hardware-software codesign

## I. INTRODUCTION

Spectre attacks exploit hardware mispredictions to coerce victim programs into transiently *transmitting* (leaking) their secret data via microarchitectural side channels, threatening the security of all programs that hold secrets in architectural state. Common *Spectre-vulnerable* (hereafter, just *vulnerable*) applications include widely-deployed cryptographic libraries [27], [34], [105], web browsers [64], [68], [88], [111], and operating system (OS) kernels [65], [67], [68], [139].

To address this threat, dozens of Spectre defenses have been proposed. They vary in the types of side channels and speculation they address, the source code modifications they require, and the classes of vulnerable programs they *target* (i.e., are tailored to protect, §III-B). Many Spectre defenses are *noncomprehensive* (§X-1). These address only specific side channels (e.g., data caches) or speculation primitives

(e.g., conditional branch prediction), leaving programs vulnerable to transient leaks involving others. Some defenses are comprehensive but *non-programmer-transparent* (§X-2). These require source code modifications, which limit their applicability and ease of adoption. *Comprehensive, programmer-transparent* defenses can fully secure vulnerable programs with minimal manual effort [13], [32], [138], [148]. Yet today, all such Spectre defenses target a single class of vulnerable programs (Tab. I), leading to performance or security limitations for other classes, which we address in this paper.

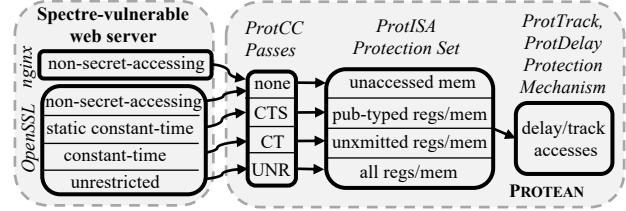

These limitations manifest for many production programs that do not fit squarely in any one of the four common classes of vulnerable code (§III-A, Fig. 2). An example is the nginx HTTPS web server (Fig. 1, left), which features code from all four classes. Because nginx contains *unrestricted* code, which *transmits* (leaks) secrets architecturally, the only prior defense capable of fully securing it is SPT’s secure baseline (SPT-SB) [32], which blocks the transient transmission of *all* architectural state. However, SPT-SB overprotects nginx’s *non-secret-accessing*, *static constant-time*, and *constant-time* components, incurring a huge and unnecessary performance hit (Tab. I). Other defenses, like STT [148] and SPT [32], that would fully secure much of nginx’s code more performantly are inadequate to fully secure the application as a whole.

### A. This Paper

We present the PROTEAN Spectre defense (Fig. 1, right), which is comprehensive, programmer-transparent, and—to address the limitations above—*programmable*. PROTEAN (1) makes its protections programmable via the *ProtISA* ISA extension (§I-A1); (2) retains programmer-transparency by automating their specification with the *ProtCC* compiler (§I-A2); and enforces them comprehensively in hardware with one of two mechanisms, *ProtDelay* or *ProtTrack* (§I-A3).

1) *Programmable ProtSets with ProtISA*: We observe that all Spectre defenses implicitly define, at each program point, a set of architectural state elements whose contents they promise to prevent from transiently leaking. We call this a

| Defense        | ProtSet        | Protection mechanism     | Vulnerable program class |     |     |      |                   |

|----------------|----------------|--------------------------|--------------------------|-----|-----|------|-------------------|

|                |                |                          | ARCH                     | CTS | CT  | UNR  | multiple (Fig. 1) |

| NDA            | all mem        | AccessDelay              | ✓                        | ✗   | ✗   | ✗    | ✗                 |

| SpecShield     | all mem        | AccessDelay              | ✓                        | ✗   | ✗   | ✗    | ✗                 |

| STT            | all mem        | AccessTrack              | 153%                     | ✗   | ✗   | ✗    | ✗                 |

| SPT            | unxmited state | AccessTrack <sup>†</sup> | ✓                        | 11% | 36% | ✗    | ✗                 |

| SPT-SB         | all state      | XmitDelay                | ✓                        | ✓   | ✓   | 187% | 177%              |

| PROTEAN (ours) | programmable   | ProtDelay                | 20%                      | 6%  | 22% | 170% | 48%               |

|                |                | ProtTrack                | 7%                       | 4%  | 16% | 169% | 32%               |

TABLE I: PROTEAN targets (§III-B) all vulnerable code classes (§III-A): non-secret-accessing (ARCH)  $\subset$  static constant-time (CTS)  $\subset$  constant-time (CT)  $\subset$  unrestricted (UNR). It secures them more performantly than class-specific defenses [13], [32], [138], [148] that target (✓/✗%), secure but do not target (✓/✗%), or do not secure (✗) them. Percentages (from Tab. V) are runtime overheads for securing vulnerable programs with the most performant available defense. <sup>†</sup>Extends AccessTrack (§VI-B2).

protection set (*ProtSet*). How a defense defines its *ProtSet* per program point dictates which vulnerable code classes it targets (i.e., is tailored to protect). Existing comprehensive, programmer-transparent Spectre defenses define their *ProtSets* via hardware-fixed rules, restricting them to target a single class (Tab. I). This limitation can be overcome by making *ProtSets* software-programmable, such that software—from any class or multiple classes—can specialize a defense’s protections to target its specific data protection needs.

To this end, PROTEAN introduces *ProtISA*, which exposes a software-programmable, hardware-tracked *ProtSet* via a single instruction prefix, *PROT*. The presence of a *PROT* prefix for an instruction specifies that its output register and input memory operands contain data that must be *protected* from transiently leaking. The absence of *PROT* indicates conversely that protection is not needed for either. For example, a prefixed *PROT* `mov rax, rdx` protects output register `rax`; an unprefixed `mov rcx, [rsp]` unprotects `rcx` and the eight bytes of memory pointed to by `rsp`. Microarchitectural support for *ProtISA* adds protection tag bits to a few structures in an out-of-order processor, plus modest logic that uses these bits to track a program’s software-defined architectural *ProtSet* as it is dynamically updated by instructions’ *PROT* prefixes.

2) *Automated ProtSet Programming with ProtCC*: Prior attempts to make hardware-tracked *ProtSets* programmable have produced non-programmer-transparent defenses, which require manual source modifications (§X-2). In contrast, we observe that *automated* compiler analyses can conservatively (for security) yet sufficiently precisely (for performance) program a *ProtSet* for code with knowledge of only its class.

Thus, PROTEAN provides the *ProtCC* compiler, which extends LLVM [74] to support automatically programming *ProtISA* with a suitable *ProtSet* for code that belongs to or combines any of the four jointly exhaustive vulnerable code classes in Fig. 2. *ProtCC* inserts no *PROT* prefixes for non-secret-accessing code, as all instruction operands are guaranteed to be public; such code runs unmodified on PROTEAN hardware. For constant-time, static constant-time, and unrestricted code, *ProtCC* runs register-only data-flow analyses to infer a conservative *ProtSet* at each program point and then inserts

Fig. 1: PROTEAN can performantly and fully secure programs containing components from different vulnerable code classes (§III-A), e.g., the nginx HTTPS web server [100], which contains unrestricted, constant-time, static constant-time, and non-secret-accessing code. Prior defenses either do not secure this program (e.g., STT [148], SPT [32]) or nonperformantly secure it *as if* all components are unrestricted (SPT-SB [32]).

*PROT* prefixes accordingly. *ProtCC* flexibly targets multi-class programs by allowing the user to specify code classes at a component (e.g., library) and/or function granularity; we do this for nginx (Fig. 1) in §VIII-B3. Also, while not our focus, *ProtCC*’s inferred *ProtSets* can be refined through source-level secrecy annotations or user-defined analyses (§V-C).

3) *Enforcing Programmed ProtSets in Hardware with ProtDelay/ProtTrack*: A Spectre defense enforces its *ProtSet* (i.e., prevents the transient transmission of its contents) via a *protection mechanism*. All comprehensive Spectre defenses feature hardware protection mechanisms [13], [32], [35], [118], [138], [146], [148], as does PROTEAN. In particular, PROTEAN features two alternative hardware protection mechanisms, *ProtDelay* and *ProtTrack*, which extend state-of-the-art mechanisms *AccessDelay* (from NDA [138]) and *AccessTrack* (from STT [148]), respectively. Not having been designed with programmable *ProtSets* in mind, *AccessDelay* and *AccessTrack* provide only partial security and incur high performance overheads when applied to *ProtISA* programs directly. *ProtDelay* and *ProtTrack* address both issues; *ProtTrack* outperforms *ProtDelay* with higher hardware complexity.

4) *Contributions*: Our main contributions are as follows:

- **ProtISA**: A novel ISA extension that exposes a software-programmable, hardware-tracked *ProtSet*.

- **ProtCC**: LLVM compiler passes that automatically program *ProtISA* to target programs that belong to one or more of the four important code classes covering all vulnerable code.

- **ProtDelay/ProtTrack**: Performant hardware protection mechanisms for comprehensively enforcing *ProtISA* *ProtSets* with different performance-complexity tradeoffs.

- **PROTEAN (ProtISA+ProtCC+ProtDelay/ProtTrack)**: A comprehensive, programmer-transparent, and programmable Spectre defense that can target any vulnerable program.

- **Security Evaluation**: We sketch a proof that PROTEAN fully secures all vulnerable programs, given an accurate classification of their components/functions. We then use an enhanced version of the AMuLeT fuzzer [41] to validate the security of PROTEAN and the three state-of-the-art Spectre defenses—STT, SPT, and SPT-SB—that serve as secure baselines in our performance evaluation, with their hardware

support all implemented in gem5. We find new gem5 side channels that leak the operands of division micro-ops and a corner-case bug in all defenses inherited from STT’s gem5 implementation [40], which we fix.

- **Performance Evaluation:** We compare the performance of PROTEAN to the above secure baselines, atop a novel gem5 hybrid-core configuration resembling an Intel Alder Lake processor, when securing various single-class programs and multi-class nginx (Fig. 1). Averaged across single-class programs, PROTEAN (ProtDelay/ProtTrack) exhibits 0.42x/0.34x the runtime overhead of the best secure baseline. For nginx, it achieves 0.27x/0.18x the runtime overhead of the only applicable secure baseline, SPT-SB. Meanwhile, it exhibits less/comparable hardware complexity.

## II. BACKGROUND

This section first provides background on hardware side-channel attacks, including Spectre attacks (§II-A). Then, we state our threat model assumptions (§II-B). Lastly, we review formal hardware-software security contracts (§II-C), which we use to validate our PROTEAN prototypes (§VII-B).

### A. Hardware Side-Channel Attacks

In a hardware side-channel attack, a *transmitter* (unsafe instruction in the victim program) modulates a *channel* (hardware resource) in an operand-dependent manner, and a *receiver* (attacker) observes the channel modulation to infer the operand value [66]. Many hardware resources have been implicated as channels, e.g., caches [106], [144], [145], branch predictors [1], [38], functional units [10], [47], memory ports [8], and others [45], [90], [109], [132], [133], [135], [140], [143]. An attacker observes channel modulations via their effects on nondeterministic aspects of program execution [55], e.g., execution time [16], [49], [106], resource contention [1], [8], [10], [90], [109], and more [11], [54], [69], [87], [115], [130].

Transient execution attacks [25] are hardware side-channel attacks that exploit hardware faults or mispredictions to steer program secrets toward the *sensitive* (leaky) operands of transient transmitters. A *transient* instruction is bound to squash [25]; a *sequential* instruction is bound to commit. *Speculative* instructions eventually become transient or sequential.

Prior work [25] classifies transient execution attacks as Meltdown [79] or Spectre [68] if they exploit faults or mispredictions, respectively. We focus only on Spectre, since Meltdown has efficient hardware or microcode mitigations on recent processors [58], including the Intel Alder Lake processor we model in §VIII.

### B. Threat Model

We assume a powerful attacker that observes a function of the data passed to transmitters’ sensitive operands (§II-B1) and can induce arbitrary speculation in the victim (§II-B2).

1) *Transmitter Assumptions:* Like the prior works that produced the secure baselines we evaluate (§VIII), we assume that load [32], [148] and store [32] micro-ops fully transmit their address operands when they execute, and conditional/indirect

branch micro-ops [32], [148] fully transmit their condition/target operand when they resolve. Unlike these works, we also assume that division micro-ops partially transmit both of their input operands when they execute (see §VII-B4b for details).

We assume these transmitters because they collectively modulate all known channels in the base gem5 O3 CPU model [21], upon which we implement PROTEAN. Our empirical security evaluation (§VII-B) flags division micro-ops as transmitters on the gem5 O3 CPU for the first time; prior work identified the others [41], [86], [148]. Nevertheless, PROTEAN is fully parametric in the set of transmitters it considers; it can be easily extended to handle new ones present on other or future CPUs to ensure a comprehensive defense.

2) *Speculation Assumptions:* Like prior work [13], [46], we consider an instruction to be speculative (i.e., possibly architectural or transient) until it reaches the head of the reorder buffer (ROB) in an out-of-order processor. We refer to this definition as the *ATCOMMIT speculation model*.<sup>1</sup> We assume *ATCOMMIT* because it is the strongest speculation model studied in prior work and captures *all types of speculation*, known [2], [3], [25], [62], [63], [111] or unknown. The weakest speculation model studied in prior work is *CONTROL* [142]. It defines an instruction to be speculative until all prior branches have resolved, modeling control-flow speculation only. In §VIII, we evaluate all defenses for all benchmarks under comprehensive *ATCOMMIT* and perform one case study under noncomprehensive *CONTROL* (§IX-A6).

### C. Hardware-Software Security Contracts

Recent work proposes formal hardware-software *security contracts*, comprising an *observer mode* and an *execution mode*, to describe which victim executions an attacker is permitted to distinguish via hardware side-channels [48]. An observer mode defines what architectural state is exposed at each victim execution step. Two observer modes, *ARCH* and *CT*, capture standard software threat model assumptions [28], [48]. *ARCH* exposes all accessed data and thus models the assumption of non-secret-accessing code (§III-A). *CT* exposes all unsafe transmitter operands and thus models the assumption of constant-time code. An execution mode defines the control-flow and data-flow paths along which a victim program exposes observations. The *SEQ* execution mode encodes sequential paths, the standard programmer assumption [48].

An *adversary model* defines how an attacker may observe channel modulations to distinguish victim program executions on a microarchitecture [48]. We adopt a powerful timing-based adversary model in §VII-B, which surfaces all transmitters assumed by our threat model (§II-B1) on the gem5 O3 CPU.

A microarchitecture *upholds* (resp. *violates*) a security contract if for all (resp. some) programs whose contract executions are indistinguishable, their microarchitectural executions

<sup>1</sup>The term *speculation model* denotes an *attack model* from prior work [32], [142], [148]. *ATCOMMIT* is equivalent to the formal definition of the *FUTURISTIC* speculation model [142], but not its prior implementations [31], [40], [141], which classify an instruction as speculative until all prior instructions executed without faulting or mispredicting. Such implementations would miss memory order speculation [111], for example.

|              |                             |                          |

|--------------|-----------------------------|--------------------------|

| <b>ARCH:</b> | <b>non-secret-accessing</b> | (unaccessed mem)         |

| <b>CTS:</b>  | <b>static constant-time</b> | (secret-typed regs/mem)  |

| <b>CT:</b>   | <b>constant-time</b>        | (untransmitted regs/mem) |

| <b>UNR:</b>  | <b>unrestricted</b>         | (all regs/mem)           |

Fig. 2: Four jointly exhaustive classes of vulnerable code we consider and what architectural state may hold secrets (in parentheses).

are indistinguishable (resp. distinguishable) per the adversary model. Existing comprehensive, programmer-transparent defenses uphold the ARCH-SEQ (NDA [138], SpecShield [13], STT [148]) or CT-SEQ (SPT [32]) security contracts. A defense that upholds ARCH-SEQ (resp. CT-SEQ) leaks no data beyond that which is accessed (transmitted) sequentially.

### III. MOTIVATING PROGRAMMABLE SPECTRE DEFENSES

This section motivates the need for a programmable Spectre defense like PROTEAN. First, we partition vulnerable programs into four classes (§III-A). Then, we survey comprehensive, programmer-transparent Spectre defenses from the perspective of our novel notion of a ProtSet (§III-B). These defenses define their ProtSets via hardware-fixed rules, restricting them to target a single program class.

#### A. Spectre-Vulnerable Program Classes

Spectre attacks threaten the confidentiality of all programs that hold secret data in architectural registers (hereafter, referred to as registers) or memory. We call such programs *Spectre-vulnerable*, or simply *vulnerable*, and divide them into four increasingly broad classes (Fig. 2)—*non-secret-accessing*, *static constant-time*, *constant-time*, and *unrestricted*—forming a hierarchy, where each class is a subset of the next.

*Non-secret-accessing (ARCH)* code does not access secrets architecturally, i.e., it never holds secrets in registers architecturally. Spectre attacks can cause ARCH code to transiently load secrets into registers and transmit them. ARCH code includes untrusted JavaScript [44] and WebAssembly [50] running in a browser and eBPF bytecode [117] running in an OS kernel. ARCH code does not leak secrets on hardware that upholds the ARCH-SEQ security contract (§II-C).

*Constant-time (CT) code* may access but does not transmit secrets architecturally, i.e., it may hold secrets in registers that are not passed to transmitters' sensitive operands architecturally. Thus, all sensitive operands of architectural transmitters exclusively hold public data. Spectre attacks can steer architecturally or transiently accessed secrets toward transient transmitters in CT code, which includes many modern cryptographic services [4], [14], [17]–[19], [22], [27], [33], [37], [39], [89], [92], [110], [114], [120], [127], [151]. CT code does not leak secrets on hardware that upholds CT-SEQ (§II-C).

*Static constant-time (CTS) code* is constant-time code that only places secrets in registers that can be *statically typed* secret per standard secrecy typing rules [29], [97], [137]. These rules mandate that all sensitive transmitter operands are publicly-typed and all instructions with secretly-typed inputs

have secretly-typed outputs. So, cryptographic declassification of secrets [122] and patterns like “`if (secret_key == 0) regenerate_key()`” are forbidden. CTS code includes explicitly-typed cryptographic code, such as code written in FaCT [29] or CT-Wasm [137] (without `declassify` operations), and untyped cryptographic code for which a valid typing is not provided but is known to exist [97], such as many primitives in OpenSSL [104] and libsodium [36].

*Unrestricted (UNR) code* refers to code that may architecturally access and transmit secrets, i.e., it can place secrets in any data register, including ones that are architecturally transmitted. Spectre attacks can coerce a non-constant-time program into transiently transmitting its secrets far more readily than the program does architecturally. Non-constant-time code includes cryptographic routines that are not written to be constant-time, including the OpenSSL [104] primitives evaluated in our UNR-Crypto suite (§VIII-B2). Also, much of the Linux kernel is non-constant-time, including page deduplication (e.g., Kernel Same-Page Merging [76]) or compression (e.g., Linux zswap [78] and zram [77]) modules.

Many important vulnerable applications span multiple classes—i.e., they are *multi-class* programs—because different components (e.g., libraries) and/or functions within the application process secret data in different ways. For example, the core logic for web servers like nginx [100] is non-secret-accessing [118], but it invokes static constant-time, constant-time, and unrestricted cryptographic primitives in OpenSSL to encrypt and decrypt network traffic (Fig. 1). As another example, the Linux kernel contains a mixture of non-secret-accessing (e.g., the ELF loader), constant-time (e.g., its cryptographic services), and unrestricted code. Spectre attacks can hijack *any* component of *any* class to transiently transmit secret data. Today's comprehensive, programmer-transparent Spectre defenses are not designed with these kind of multi-class programs in mind and thus exhibit performance or security limitations when defending them (Tab. I).

#### B. Protection Sets and Protection Mechanisms

We observe that all Spectre defenses implicitly define a *protection set (ProtSet)* and a *protection mechanism*. A defense's ProtSet may evolve as a program executes and contains, at each architectural execution step, the set of architectural state elements that the defense promises to prevent from transiently leaking. We say that a defense *protects* data in its ProtSet and *unprotects* data outside of it. A defense's protection mechanism is responsible for enforcing its ProtSet, i.e., ensuring that no data in the set transiently leaks.

A Spectre defense *secures* a particular program class (§III-A, Fig. 2) if for each architectural execution step of each program in the class, the defense's ProtSet always contains all architectural state elements that may hold secret data (in parentheses in Fig. 2). Because the four vulnerable program classes we identify form a hierarchy with respect to which subsets of architectural state may hold secrets, if a defense secures a broader program class (e.g., CT code), it also secures all narrower classes (e.g., CTS and ARCH code).

We say a defense *targets* a program class if it secures that class but not the next broader class in the hierarchy. This notion approximates how precisely a defense’s ProtSet aligns with a program’s protection needs. We find that defenses that target a class outperform those that merely secure it (Tab. I).

### C. Hardware-Defined ProtSets (Prior Work)

Existing comprehensive, programmer-transparent Spectre defenses (Tab. I) define their ProtSets via hardware-fixed rules, so each exclusively targets *one* program class. STT [148], NDA [138], and SpecShield’s [13] ProtSets always include all memory but no registers, so they target ARCH programs and secure no others (Fig. 2). SPT’s ProtSet always includes all registers and memory bytes that have not been architecturally transmitted in the past by being passed to the sensitive operand of a transmitter, directly or indirectly via invertible arithmetic dependencies [32]. Thus, it targets CT programs and secures, but does not target, CTS and ARCH programs. SPT-SB’s ProtSet always includes all registers and memory bytes [32]. Hence, it secures all four classes, but targets only UNR.

There is no comprehensive, programmer-transparent Spectre defense that targets multi-class programs (§III-A). Such a defense must be able to independently target each of these programs’ constituent single-class components/functions, which is not possible with hardware-defined ProtSets.

### D. Software-Programmable ProtSets (This Paper)

Rather than defining its ProtSet in hardware, our proposed PROTEAN Spectre defense makes its ProtSet *software-programmable*. Doing so enables it to target vulnerable programs of *all* classes, including those that are multi-class. In particular, PROTEAN consists of: ProtISA, an ISA extension that exposes a software-programmable, hardware-tracked ProtSet (§IV); ProtCC, a compiler that automatically, programmer-transparently programs it (§V); and ProtDelay and ProtTrack, two alternative hardware protection mechanisms that comprehensively enforce it (§VI).

## IV. PROTISA

This section presents *ProtISA*, a novel ISA extension that exposes a programmable ProtSet (§IV-A) to software with a single new instruction prefix, PROT (§IV-B), and tracks this ProtSet in hardware with modest microarchitectural support (§IV-C). We introduce ProtISA for x86, as it is the only major ISA with instruction prefixes. However, ProtISA can be extended to work with any major ISA by storing PROT prefixes separately in an instruction metadata table [65]. Note that ProtISA simply enables software to define an architectural ProtSet for hardware to track. This is distinct from the AccessTrack/ProtTrack taint tracking protection mechanisms in §VI, which use ProtISA to identify access instructions.

### A. Requirements for Programmable ProtSets

Our goal for ProtISA is to expose a ProtSet to software that compiler analyses can program automatically. Such compiler analyses (e.g., in §V-A and prior work [30], [97]) infer at each

program point which accessed registers and memory bytes hold potentially secret or definitely public data. So, to program a ProtSet, these analyses need the ability to dynamically:

- 1) add/remove individual secret/public (a) registers and (b) memory bytes to/from the ProtSet when they are written to, i.e., protect/unprotect secret/public data when it is produced; and

- 2) remove individual public (a) registers and (b) memory bytes from the ProtSet when they are read from, i.e., unprotect (declassify) data that is newly inferred to be public some time after it has been produced.

Note that marking individual registers and memory bytes as protected when they are read from (i.e., classifying data some time after it has been produced) is futile and thus not a requirement. If data was previously protected, this does nothing. If previously unprotected, it may have already transiently leaked.

### B. Programming a ProtSet with PROT

To satisfy the requirements above, ProtISA introduces a single new instruction prefix, PROT. *PROT-prefixed* instructions dynamically add their output registers to ProtISA’s ProtSet, i.e., label them *protected*. *Unprefixed* instructions remove their output registers and any read memory bytes from the ProtSet, i.e., label them *unprotected*. Stores label written memory bytes protected/unprotected according to the protection of their data operand. ProtISA tracks protections at full register granularity; subregisters (e.g., `a1`) inherit the protection of their corresponding full register (e.g., `rax`). For instructions that decode into multiple micro-ops, each micro-op inherits any PROT prefix on the instruction, and ProtISA’s semantics are applied to each micro-op individually.

These simple and straightforward semantics offer surprising flexibility for software programming of a ProtSet. Below, we demonstrate how judicious use of PROT (or its absence) can achieve all required capabilities in §IV-A. We color-code *protected/unprotected* output registers and *unprotected* input memory in following examples and figures (Figs. 3 and 4).

- 1) *Protect/unprotect register writes (req. 1a):* To protect or unprotect the explicit (e.g., `rax`) and implicit (e.g., `rflags`) output registers of an instruction, PROT-prefix the instruction (left below) or do not (right).

```

PROT add rax, rdx      | add rax, rdx

// rax, rflags protected | // rax, rflags unprot

```

We conservatively handle subregister updates for unprefixed (resp. PROT-prefixed) instructions like (PROT) `mov al, bl` by not modifying the protection of (resp. protecting) the full output register, in this case `rax`.

- 2) *Protect/unprotect memory writes (1b):* The memory bytes written to by a store are protected or unprotected if its data operand is protected (left below) or unprotected (right).

```

// rax prot      | // rax unprot

PROT add [rsp], rax | mov [rsp], rax

// rax, [rsp], rflags prot | // rax, [rsp] unprot

```

A PROT prefix has no effect on a store unless it contains an internal load or arithmetic micro-op, which inherits the PROT prefix (left above).

3) *Unprotect register reads (2a)*: To unprotect an instruction’s input register (e.g., the data operand of the store `mov [rsp], rax` above), prepend an unprefixed identity register move (e.g., `mov rax, rax`). Register moves are cheap on modern hardware due to move elimination [60].

4) *Unprotect memory reads (2b)*: To unprotect the memory read by a load, leave the load unprefixed (left below). However, PROT-prefixing a load does not protect the memory it reads (right), as doing so would be futile (§IV-A).

```

mov rax, [rsp]           | prot mov rax, [rsp]

// rax, [rsp] unprotected | // rax protected

```

### C. Microarchitectural Support for ProtISA

ProtISA tracks its software-programmed, architectural ProtSet in a speculative, out-of-order microarchitecture by dynamically tagging three types of state with protection bits: rename map entries, load-store queue (LSQ) entries, and L1 data cache (L1D) lines. A set/reset protection bit indicates the tagged state is architecturally protected/unprotected.

1) *Tracking Register Protection*: ProtISA tracks its register ProtSet by extending each rename map entry with a protection bit. When an instruction is renamed, ProtISA updates the rename map entry of each output register with its allocated physical register identifier and marks the entry protected/unprotected if the instruction is PROT-prefixed/unprefixed.

2) *Tracking Memory Protection*: Precisely tracking memory protections would require a shadow memory [146], which is impractical [32]. Instead, ProtISA conservatively tracks its memory ProtSet through the LSQ and L1D only, as follows.

a) *Protection-tagged L1D*: Like SPT [32], we extend each byte in the L1D with one protection bit. Any memory bytes not present in the L1D (or LSQ) are assumed protected, i.e., L1D evictions cause ProtISA to forget what data was unprotected. L1D protection bits require  $48 \text{ KiB}/8 = 6 \text{ KiB}$  per Intel Alder Lake P-core and  $32 \text{ KiB}/8 = 4 \text{ KiB}$  per E-core in our evaluation (§VIII). Cacti [12] approximates the area required for a parallel L1D protection bit array for 22 nm technology (Cacti does not support Alder Lake’s 10 nm) at  $0.0418/0.0292 \text{ mm}^2$  for P-cores/E-cores, introducing 1.4% area overhead for a P-core/E-core’s  $3.0560/2.1527 \text{ mm}^2$  L1D.

b) *Protection-tagged LSQ*: Each LSQ entry is tagged with a single protection bit, indicating the protection of accessed memory bytes.

At execute, stores copy their data operand’s protection bit into their LSQ entry’s protection bit. At writeback, stores copy their LSQ entry’s protection bit to the L1D protection bits corresponding to the written bytes.

Also at execute, loads either read from the L1D or forward from a store in the LSQ. An L1D load sets its LSQ entry’s protection bit to the logical OR of the L1D protection bits of the bytes it reads. Forwarding loads simply copy both the protection bit from the store’s LSQ entry into their own. At commit, loads with unprotected outputs clear the protection bit of all accessed memory bytes in the L1D.

### D. Security Properties of ProtISA

Attackers cannot use ProtISA to architecturally unprotect victim secrets due to two key properties. First, an attacker cannot use ProtISA to architecturally unprotect (via an unprefixed instruction) architecturally inaccessible data, like data outside its sandbox. Second, ProtISA embeds the ProtSet directly into executable code (as PROT is an instruction prefix). An attacker cannot architecturally tamper with another program’s ProtSet (e.g., by removing PROT prefixes or triggering out-of-bounds unprefixed loads) unless it can first overwrite or hijack victim code, a more severe security concern [125].

An attacker cannot use transient execution (e.g., by transiently jumping to an unprefixed load of secret memory) to architecturally unprotect registers or memory, since instructions only update protections on retired state when they commit. An attacker cannot exploit race conditions on shared memory accesses to improperly unprotect it, since ProtISA’s memory protection tags shadow the L1D, which maintains coherence.

### E. ProtISA’s Interface with Protection Mechanisms

ProtISA’s purpose is to enable software to tell hardware protection mechanisms (§III-B) what architectural state requires protection from (transient) hardware side-channel leakage. Thus, ProtISA must expose protection tags throughout the entire pipeline, including the out-of-order backend where transmitters execute/resolve (§II-B1). While ProtISA’s tagging of the LSQ and L1D already exposes protection bits to the backend, its tagging of the rename map does not. Thus, at rename time, ProtISA also tags each renamed input and output physical register operand with its rename map entry’s protection tag. Note that PROTEAN’s hardware protection mechanisms (§VI) enforce that no data that ProtISA architecturally protects leaks *transiently*; future work could also prevent this data from leaking *architecturally* (akin to [146]).

## V. PROTCC

This section presents *ProtCC*, a set of compiler passes that can automatically and programmer-transparently program ProtISA ProtSets to target any of the four classes of vulnerable code in Fig. 2. We explain ProtCC’s passes (§V-A), compilation requirements (§V-B), and possible extensions (§V-C).

### A. ProtCC Passes

ProtCC features four passes (one trivial), whose outputs are shown in Fig. 3b-e for an example program in Fig. 3a. ProtCC accommodates both single- and multi-class programs by allowing each component/function to be instrumented independently according to its corresponding (single) class (§III-A), which the user specifies via ProtCC compilation flags.

1) *ProtCC-ARCH (no-op)*: Securing non-secret-accessing (ARCH) programs requires protecting architecturally unaccessed memory. Unmodified binaries, lacking PROT prefixes, naturally program this ProtSet by unprotecting only architecturally accessed memory. So, ProtCC-ARCH is a no-op pass.

```

static int A[];

int foo(int *p) {

x = *p;

y = 0;

if (x >= 0)

y = A[x];

return y;

}

(a) C source

<foo>: # CT

1 mov Rp, Rp

2 PROT mov Rx, [Rp]

3 mov Ry, 0

4 PROT cmp Rx, 0 #rflags

5 jl .skip #rflags

6 mov Rx, Rx

7 PROT mov Ry, [A+Rx]

.skip: ret

(b) ProtCC-ARCH

<foo>: # ARCH

1 mov Rx, [Rp]

2 mov Ry, 0

3 cmp Rx, 0 #rflags

4 cmp Rx, 0 #rflags

5 jl .skip #rflags

6 PROT mov Ry, [A+Rx]

.skip: ret

(c) ProtCC-CTS

<foo>: # CTS

1 mov Rp, Rp

2 mov Rx, [Rp]

3 mov Ry, 0

4 PROT cmp Rx, 0 #rflags

5 jl .skip #rflags

6 PROT mov Ry, [A+Rx]

7 PROT mov Ry, [A+Rx]

.skip: ret

(d) ProtCC-CT

<foo>: # UNR

1 PROT mov Rx, [Rp]

2 mov Ry, 0

3 PROT cmp Rx, 0 #rflags

4 jl .skip #rflags

5 PROT mov Ry, [A+Rx]

6 PROT mov Ry, [A+Rx]

7 PROT mov Ry, [A+Rx]

.skip: ret

(e) ProtCC-UNR

```

Fig. 3: Assembly output for each ProtCC pass on example code. Instructions or **PROT** prefixes inserted by ProtCC are **bold**.

2) *ProtCC-CTS*: Recall that static constant-time (CTS) programs only place secrets in registers that can be statically typed secret per standard secrecy typing rules (§III-A). Thus, ProtCC-CTS can automatically infer a conservative secrecy typing for CTS code, *without* access to explicit secrecy labels, by: (i) initializing all registers to be secretly-typed and then iteratively (ii) applying such standard secrecy typing rules and (iii) resolving type errors by retyping the culprit register as public, until convergence. The authors of Serberus, a software Spectre defense [97], prove that this approach is guaranteed to find a conservative secrecy typing of the program (i.e., all secrets are typed as such). Specifically, our implementation of ProtCC-CTS applies type rules 2, 6, 7, 8 in Definition 4.5 of the Serberus paper. By forgoing its other type rules (which are specific to the strict subclass of CTS code Serberus considers), ProtCC-CTS may secretly-type some registers that Serberus will publicly-type, but never vice versa.

After inferring which registers are secretly-typed, ProtCC-CTS **PROT**-prefixes all instructions that define a secretly-typed register. Then, it inserts identity moves (§IV-B3) to architecturally unprotect each publicly-typed argument at function entry, ensuring all registers that may hold secrets are protected. To see why all secret memory is protected, recall again that memory can only be unprotected by an architectural load/store to/from an unprotected and therefore publicly-typed output/data register. Such memory must also hold public data.

*Example (Fig. 3c):* ProtCC-CTS initially types Rx secret, but changes it to public, because it is passed to the transmitter on line 6 (a load) along some control-flow path. At convergence, ProtCC-CTS types the definitions of Rp, Rx, Ry (line 3) as public and the definition of Ry (line 6) as secret. Thus, ProtCC-CTS inserts an identity move to unprotect Rp on line 1 and **PROT**-prefixes the (re)definition of Ry on line 6.

3) *ProtCC-CT*: Recall that constant-time (CT) programs never place secrets in registers that are architecturally fully (or partially) transmitted (§II-B1). Thus, ProtCC-CT can safely

unprotect all registers that were fully transmitted in the *past* or will be in the *future* architectural execution. Based on this observation, ProtCC-CT implements two register-level data-flow analyses to compute the set of registers at each architectural program point that already fully leaked (or hold constant data) along all prior control-flow paths or are bound to leak along all future control-flow paths.

ProtCC-CT then (i) **PROT**-prefixes all instructions with any output register (including rflags) that is neither past-leaked nor bound-to-leak and (ii) inserts an identity move (§IV-B3) along every control-flow edge on which a register becomes newly bound-to-leak in order to label it unprotected. Case (i) ensures all registers that may hold secrets are protected, and case (ii) architecturally declassifies a previously protected register once it must hold public data.

*Example (Fig. 3d):* ProtCC-CT analyses find that Rp is bound-to-leak on function entry and Rx becomes bound-to-leak along the not-taken direction of the branch (line 5→6) since it will be architecturally transmitted by the load on line 7. Thus, ProtCC-CT inserts identity moves on lines 1 and 6 to unprotect Rp and Rx, respectively. Ry becomes past-leaked after line 3, since it holds constant data. However, Ry is no longer past-leaked when overwritten by the load on line 7; thus, ProtCC-CT **PROT**-prefixes it.

4) *ProtCC-UNR*: Recall that unrestricted programs may place secrets in any data register, including those that are fully transmitted (§III-A). Thus, we can only unprotect registers that *never* hold secret program data. Such registers include the *stack pointer* (e.g., rsp on x86), registers initialized with a constant, and registers computed solely from them (e.g., the frame pointer, or loop indices starting at 0). ProtCC-UNR **PROT**-prefixes all instructions with output registers except those whose output registers are one of the aforesaid registers.

*Example (Fig. 3e):* ProtCC-UNR only unprotects the zero-initialization of Ry on line 2, but **PROT**-prefixes all other instructions and thus protects all other registers and memory.

### B. ProtCC Compilation Requirements

All secret-accessing code loaded into the address space, including any secret-accessing shared libraries and JITed code, must be compiled with the appropriate ProtCC pass. This protects all architectural state that may hold secret data. Failing to recompile such code allows secret data to leak transiently, even with PROTEAN’s defenses enabled. Non-secret-accessing code does not require recompilation (§V-A1).

Code of an unknown class has multiple compilation options. For users that want PROTEAN to *guarantee* that no secrets will leak, it must be compiled with ProtCC-UNR, at a high performance cost (§IX). Users willing to permit transient leakage of a *formally bounded* amount of secret information for performance can compile code with ProtCC-CT to uphold CT-SEQ (§II-C), ProtCC-CTS to uphold CTS-SEQ (§VII-B), or forgo recompilation to uphold ARCH-SEQ (§II-C).

### C. Possible ProtCC Extensions

Users willing to trade programmer transparency for additional performance can refine the ProtSets inferred by ProtCC

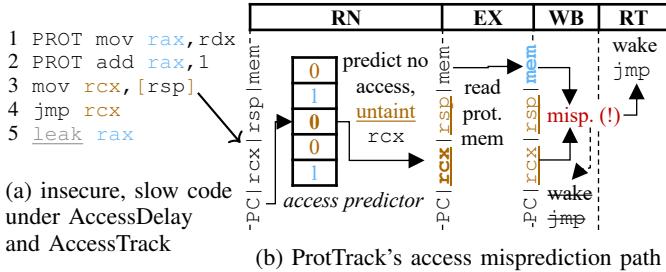

Fig. 4: ProtDelay/ProtTrack, but not AccessDelay/AccessTrack, secure the code in (a) by stalling the `transient` access transmitter (line 5). For performance, ProtDelay speculatively wakes up line 2, and ProtTrack predicts line 3 is not an access, safely handling mispredictions as shown in (b).

through manual annotations or custom ProtCC passes. For the former, ProtCC can be extended to support the explicit annotation of variables, expressions, and memory as public. For the latter, users can either extend one of ProtCC’s existing passes or provide a new pass entirely.

## VI. PROTDELAY AND PROTTRACK

This section introduces the *ProtDelay* and *ProtTrack* hardware protection mechanisms, which PROTEAN uses to performantly and comprehensively enforce ProtISA ProtSets. *ProtTrack* optimizes for performance at the cost of higher hardware complexity; *ProtDelay* makes the opposite tradeoff.

### A. Applying Access-Based Defenses to ProtISA ProtSets

*ProtDelay* and *ProtTrack* extend state-of-the-art hardware protection mechanisms that *delay* waking up the dependents of (AccessDelay, §VI-A1) or *taint-track* the outputs of (AccessTrack, §VI-A2) speculative *access instructions*, respectively. AccessDelay and AccessTrack (our terms) define access instructions as those that read potential secrets into output registers [148] and typically assume they are loads [13], [138], [148]. For ProtISA hardware, we define them as follows:

**Definition 1.** On ProtISA hardware, *access instructions* are instructions with protected register or memory inputs.<sup>2</sup> *Access transmitters* are both access instructions and transmitters (§II-A) and have a protected sensitive input.

As we discuss next, applying AccessDelay or AccessTrack *directly* to ProtISA’s access instruction definition results in a partial and nonperformant defense, since these mechanisms were not designed with programmable ProtSets in mind.

1) *AccessDelay*: NDA and SpecShield propose the *AccessDelay* protection mechanism [13], [138], which allows all access instructions to execute and write back speculatively, but forbids them from waking up dependents until the access becomes non-speculative. This prevents transient access instructions (e.g., the `add` in Fig. 4a) from propagating their protected data inputs to dependent transmitters (e.g.,

<sup>2</sup>ProtISA’s definition of access instruction admits stores, whereas prior work’s does not [148] because stores lack an output register.

the `leak` in Fig. 4a), which is sufficient to secure non-secret-accessing programs (NDA’s and SpecShield’s target). However, it does not prevent access transmitters (e.g., `leak` `rax`) from transmitting their own protected sensitive input (e.g., `rax`), a security violation for ProtISA programs, which can access secrets.

Furthermore, AccessDelay unnecessarily blocks speculative PROT-prefixed access instructions (e.g., PROT `mov rax, rdx` in Fig. 4a) from waking their non-transmitter dependents (e.g., PROT `add rax, 1`), a performance issue. Such dependents can safely execute speculatively, since they re-access the protected register produced by the PROT-prefixed access. That is, such dependents are themselves speculative access instructions, whose wakeup of dependents AccessDelay will delay as needed.

2) *AccessTrack*: STT proposes the *AccessTrack* protection mechanism, which taints the output registers of access instructions and their dependents at rename, untainting them once the youngest access instruction they depend on becomes non-speculative [148]. AccessTrack delays the execution/resolution of transmitters with tainted sensitive inputs (§II-B1) until untainted. Like AccessDelay, AccessTrack allows access transmitters to transiently transmit untainted, yet protected, input registers, which do not arise in non-secret-accessing programs (STT’s target) but do arise in ProtISA programs. For example, AccessTrack taints output `rax` of the access instruction PROT `add rax, 1` and thus delays `leak rax`’s transmission of its tainted input. However, AccessTrack untaints `rax` once the `add` retires, allowing `leak` to transiently transmit its untainted but still protected input, `rax`, a security violation for ProtISA.

Plus, while AccessTrack requires identifying access instructions at rename, ProtISA cannot determine whether loads read protected memory until they execute. So, AccessTrack must conservatively taint the outputs of *all* loads. Its untaint broadcast logic [148] can further only untaint output registers at commit, preventing early recovery from false positives that read unprotected memory. Both are performance issues.

### B. Adapting Access-Based Defenses for ProtISA ProtSets

ProtDelay and ProtTrack augment AccessDelay and AccessTrack, respectively, to extend their security guarantees to and improve their performance on ProtISA programs, as follows.

1) *ProtDelay*: For security, ProtDelay extends AccessDelay to additionally delay the transmission of access transmitters’ protected sensitive operands, until they are non-speculative.

For performance, ProtDelay relaxes AccessDelay’s wakeup delay logic to only delay wakeup of the dependents of unprefixed, but not PROT-prefixed, accesses. This is safe because ProtDelay will delay these dependent access instructions anyway, either in their execution/resolution if they are access transmitters or in their wakeup of dependents otherwise.

2) *ProtTrack*: For security, ProtTrack extends AccessTrack to also delay the speculative execution/resolution of access transmitters, like ProtDelay. SPT augments AccessTrack in the same way to target constant-time programs [32].

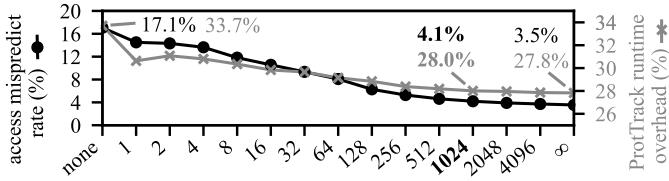

Fig. 5: ProtTrack access predictor sensitivity study (x-axis: number of predictor entries; we choose  $n = 1024$ ). The access misprediction rate is the fraction of retired non-PROT-prefixed loads with unprotected outputs for which ProtTrack’s access predictor guesses incorrectly at rename whether the load reads protected memory at execute. ProtTrack’s runtime overhead is averaged across ProtCC-ARCH-/ProtCC-CT-compiled SPEC2017int benchmarks on our P-core configuration (§VIII-A), normalized to an unsafe baseline.

For performance, ProtTrack untaints loads that are predicted to read unprotected memory (§VI-B2a), ensuring security by falling back to ProtDelay when the prediction is wrong or an untainted load forwards from a tainted store.

a) *Secure Access Predictor*: ProtTrack uses a simple 1-bit predictor table with  $n = 1024$  untagged entries, indexed by the 10 least significant bits of load program counters (PCs). Each entry stores whether a load accessed protected memory the last time it executed. The total predictor size is  $1024/8 = 128$  bytes. We choose  $n = 1024$  entries because our predictor sensitivity study (Fig. 5) shows that it attains a misprediction rate within 0.6% and a runtime overhead within 0.2% of an infinitely-sized predictor.

ProtTrack predicts whether a load is an access instruction at rename time as follows. First, it indexes into the access predictor. If the load’s entry is *no-access* and its output is unprotected (computed in parallel by ProtISA also at rename, §IV-C1), ProtTrack predicts the load will not be an access instruction and predictively untaints the load’s output (Fig. 4b). Otherwise, ProtTrack taints the load’s output, as it is predicted to read protected memory.

b) *Secure Misprediction Recovery*: ProtTrack’s access predictor can generate two types of mispredictions: *false negatives*, which predict *no-access* for a load that reads protected memory and are a security risk; and *false positives*, which predict *access* for a load that reads unprotected memory but are benign aside from reducing performance. ProtTrack handles false negatives by falling back to ProtDelay, i.e., delaying the wakeup of all non-access dependents until the load retires. This ensures mispredictions never cause data to speculatively propagate from protected memory to an untainted, unprotected register. Empirically, both types of mispredictions are rare (Fig. 5). We update the predictor with the load’s actual access outcome (1 for *access*, 0 for *no-access*) when it retires.

c) *Secure Tainted Store Forwarding*: ProtTrack also falls back to ProtDelay for untainted loads that forward from stores of tainted data, but only stalls the load’s wakeup of dependents until the store’s data operand becomes untainted (rather than until the load commits). This prevents attackers from circumventing ProtTrack’s register taint tracking by speculatively storing and reloading tainted data to/from memory.

3) *Threat Model Considerations*: ProtDelay and ProtTrack comprehensively block all transient leakage of protected data via all hardware side channels due to all types of speculation, since they are fully parametric in their assumed transmitters and adopt the ATCOMMIT speculation model (§II-B).

## VII. SECURITY EVALUATION

This section evaluates PROTEAN’s security. First, we sketch a proof that for all single- or multi-class programs (§III-A), PROTEAN blocks all transient leakage of secrets and thus all Spectre attacks [25] (§VII-A). Then, we empirically validate that our gem5 [21] prototypes of PROTEAN hardware uphold one security contract for arbitrary ProtISA binaries and one of three others for single-class ProtCC binaries (§VII-B).

### A. Formal Security Proof Sketch

ProtCC ensures that the architectural ProtISA ProtSet always contains all architectural state that may hold secret data:

**Lemma 1.** *Given a program and a class-labeling of its functions/components, ProtCC programs ProtISA (via PROT prefixes) to always protect all architectural state that may hold secret data in all of the program’s architectural executions.*

*Proof sketch.* See class-specific arguments in §V-A.

Then, ProtISA’s hardware support tags protected all architectural state in ProtISA’s architectural ProtSet (and thus all secret data, by Lem. 1):

**Lemma 2.** *The set of retired architectural registers and memory bytes that ProtISA’s hardware support tags protected is a superset (due to implicitly tagging memory bytes outside the LSQ/LID as protected) of those in ProtISA’s ProtSet.*

*Proof sketch.* See ProtISA’s hardware implementation (§IV-C).

Lastly, ProtDelay/ProtTrack block the transient transmission of all architectural state that is tagged protected by ProtISA’s hardware support (and thus all secret data, by Lem. 2):

**Lemma 3.** *ProtDelay/ProtTrack prevent the transient transmission of data derived from retired protected-tagged state.*

*Proof sketch.* Such data can only leak via a transmitter’s sensitive operand. If protected, ProtDelay/ProtTrack block its transmission until the transmitter retires (§VI-B). If unprotected, such data must depend on a speculative access instruction with an unprotected output. In this case, ProtDelay/ProtTrack block the data’s transmission until the access instruction retires—at which point the data is officially architecturally unprotected.

**Theorem 4.** *Given a program and a class-labeling of its functions/components, PROTEAN prevents all transient leakage of secrets in all of the program’s speculative executions.*

*Proof sketch.* By Lems. 1 and 2, the ProtISA microarchitecture tags protected all retired architectural state holding secret data. By Lem. 3, ProtDelay/ProtTrack prevent all retired protected state from leaking transiently. Thus, the combination, PROTEAN, prevents all transient leakage of secrets.

| Contract   | Instrumentation | Violations, out of 200 |               |               |

|------------|-----------------|------------------------|---------------|---------------|

|            |                 | Unsafe                 | PROTEAN       |               |

|            |                 |                        | ProtDelay     | ProtTrack     |

| UNPROT-SEQ | ProtCC-RAND     | <b>189</b> (1)         | <b>0</b> (0)  | <b>0</b> (0)  |

| ARCH-SEQ   | ProtCC-ARCH     | <b>200</b> (0)         | <b>0</b> (2)  | <b>0</b> (5)  |

| CTS-SEQ    | ProtCC-CTS      | <b>200</b> (0)         | <b>0</b> (1)  | <b>0</b> (0)  |

| CT-SEQ     | ProtCC-CT       | <b>200</b> (0)         | <b>0</b> (16) | <b>0</b> (10) |

| CT-SEQ     | ProtCC-UNR      | <b>199</b> (1)         | <b>0</b> (20) | <b>0</b> (17) |

TABLE II: AMuLeT\*-detected contract violations for ProtCC-RAND/-ARCH/-CTS/-CT/-UNR test binaries on unsafe, ProtDelay, and ProtTrack hardware. False positives (§VII-B1) are in parentheses.

### B. Empirical Security Evaluation with AMuLeT\*

We empirically assess the security of our gem5 prototypes of PROTEAN (ProtISA with ProtDelay/ProtTrack) and those of the secure baselines (STT [40], SPT [31], and SPT-SB [31]) that we compare PROTEAN’s performance to in §VIII.

1) *AMuLeT\**: We conduct this evaluation with AMuLeT\*,<sup>3</sup> which extends AMuLeT [41], a fuzzing framework for testing gem5 implementations of Spectre defenses against §II-C-style security contracts, with the following enhancements:

a) *New test generator*: Adds a new LLVM-IR test generator based on llvm-stress [85]. Unlike the assembly tests that AMuLeT generates, these IR tests can be compiled by ProtCC.

b) *Enhanced CT observer mode*: Extends AMuLeT’s CT observer mode, which exposes instructions’ PCs and accessed addresses, to also expose individual address registers,<sup>4</sup> matching our and prior defenses’ transmitter assumptions (§II-B1).

c) *New observer modes*: Adds new UNPROT and CTS observer modes, which further extend CT to also expose all data held in ProtISA-unprotected and publicly-typed (§III-A) registers, respectively. These observer modes enable testing PROTEAN against the UNPROT-SEQ and CTS-SEQ contracts.

d) *New adversary model*: Adds a new adversary model (§II-C) that exposes to an attacker the cycle at which each instruction reaches each pipeline stage. This adversary model surfaces contract violations in STT/SPT/SPT-SB that AMuLeT’s default cache+TLB adversary model does not, since it exposes fine-grained secret-dependent timing information observable to SMT receivers.

e) *False positive detection*: Largely automates detection of false-positive contract violations (§II-C) during post-processing. While AMuLeT filters false positives during fuzzing, it does not do so during post-processing. AMuLeT\* classifies a contract violation as a false positive if the committed microcode sequences of the violating microarchitectural executions differ in their PCs or accessed addresses—indicating *sequential*, not transient, leakage. Such cases arise due to AMuLeT bugs or identical committed instruction sequences taking divergent microcode paths.

2) *Experimental Setup*: We use AMuLeT\* to test the security of a series of (gem5 hardware configuration, ProtCC pass, security contract) triples. For each triple, we run 200 parallel

instances of AMuLeT\*, with each instance configured to randomly generate 200 LLVM-IR programs, instrumented with the triple’s ProtCC pass. For 100 of the AMuLeT\* instances, we test 140 random inputs per program under AMuLeT\*’s default adversary model, which exposes data cache and TLB tags. For the other 100 instances, we test 5 inputs per program under our timing-based adversary model (§VII-B1). In total, we test up to  $100 \times 200 \times (140 + 5) = 2,900,000$  executions per triple. Each AMuLeT\* instance exits upon detecting its first contract violation or completing all tests.

3) *Evaluated Hardware Configurations*: To validate AMuLeT\* itself, we use it to test the unmodified gem5 O3 CPU (base commit 8381e1c), our unsafe baseline in §VIII.

To validate the security of the gem5 implementations of PROTEAN and the secure baselines, we base PROTEAN’s and rebase STT/SPT/SPT-SB’s onto the same aforesaid commit and configure all to adopt the ATCOMMIT speculation model (§II-B2). We then run AMuLeT\* on them all in two stages. First, we configure all defenses to assume that loads, stores, and branches are transmitters, as these are the only gem5 transmitters documented in prior work (§II-B1). During early testing, AMuLeT\* discovers a new transmitter (division micro-ops) and a new bug in all defense implementations. So, we extend all defense implementations to treat division micro-ops as transmitters and also apply a bug fix to them. Then, we rerun AMuLeT\* on the fixed defense implementations, which we evaluate in §VIII.

4) *Experimental Results*: Tab. II presents final testing results for the unsafe baseline and PROTEAN specifically. We describe AMuLeT\*’s findings for all experiments next.

a) *Unsafe baseline*: We use AMuLeT\* to test the unsafe baseline against all security contracts with all ProtCC passes. As expected, it detects hundreds of violations for each contract (Tab. II). We expect most are true positives, since AMuLeT\* filters many false positives (§VII-B1); however, due to their sheer quantity, we do not manually validate them all as such.

b) *PROTEAN*: We validate that PROTEAN upholds UNPROT-SEQ for ProtISA binaries and ARCH-/CTS-/CT-SEQ for ProtCC-ARCH/-CTS/-CT binaries. To obtain random ProtISA binaries for testing against UNPROT-SEQ, we compile each test with a ProtCC pass (designed for testing) that PROT-prefixes a random subset of instructions (ProtCC-RAND in Tab. II). PROTEAN upholds a stronger security property on ProtCC-UNR binaries than any §II-C-style security contract can capture, as such contracts assume sequentially-leaked data is always public, but in unrestricted code, it may be secret (§III-A). So, we test PROTEAN against CT-SEQ, the strongest contract implemented in AMuLeT\*, on ProtCC-UNR binaries.

**Early testing results:** While testing an early implementation of PROTEAN, AMuLeT\* uncovered two security issues that also impact all three secure baselines (STT/SPT/SPT-SB).

First, it detected that division micro-ops leak a function of their  $n$ -bit divisor and  $2n$ -bit dividend on the gem5 O3 CPU by conditionally faulting if the divisor is zero or the  $2n$ -bit quotient overflows the  $n$ -bit output register. No prior work has found that division micro-ops are transmitters on gem5.

<sup>3</sup>AMuLeT\*: <https://github.com/StanfordPLArchSec/protean-amulet.git>.

<sup>4</sup>x86 memory operands can have two address registers, e.g., `mov rax, [rsp+rdi]`. AMuLeT exposes the sum `rsp+rdi`; AMuLeT\* exposes `rsp` and `rdi` individually.

Second, AMuLeT\* found a previously unknown corner-case bug in PROTEAN’s implementation of delayed branch resolution, which it borrows directly from STT/SPT/SPT-SB. In this implementation, the execute stage notifies the commit stage of the youngest branch misprediction detected in that cycle, regardless of whether it is tainted/protected or untainted/unprotected. As a result, an older tainted/protected branch can conditionally block a younger untainted/unprotected branch from initiating a squash depending on whether the former was mispredicted. This creates a secret-dependent squash signal that leaks the tainted/protected branch predicate. To restore security, we patched PROTEAN and upstreamed fixes to STT [96] and SPT/SPT-SB [93] to instead separately notify the commit stage of the youngest *untainted/unprotected* branch misprediction and *all* tainted/protected branch mispredictions detected a given cycle.

**Final testing results:** AMuLeT\* finds zero true-positive contract violations in our final, fixed gem5 implementation of PROTEAN, out of 28.3 million executed tests. We evaluate the performance of this implementation of PROTEAN in §VIII.

*c) STT, SPT, and SPT-SB:* Like prior work [41], we test STT and SPT against the ARCH-SEQ and CT-SEQ contracts, respectively, on unmodified binaries. We also test SPT-SB against CT-SEQ on unmodified binaries, for reasons discussed in §VII-B4b. We set a four-hour time limit for AMuLeT\* instances, due to STT/SPT/SPT-SB’s high host runtimes.

**Early testing results:** AMuLeT\* finds 9/31/65 true-positive contract violations for STT/SPT/SPT-SB before patching them to fix the two security issues found in §VII-B4b.

**Manual inspection results:** We manually discover a corner-case implementation bug in SPT that AMuLeT\* misses, which causes the defense to improperly untaint the output register and input memory of secret-accessing transient loads following a pending fault. SPT’s implementation untaints the output registers of loads (and all other instructions) at rename before later tainting them upon insertion into the ROB. When a fault reaches commit and initiates a machine clear, the O3 CPU stops inserting dispatched (now transient) instructions into the ROB. Crucially, however, it may still insert loads into the LSQ and execute them. Because these loads bypass ROB insertion, their outputs remain incorrectly untainted. So, when they compute their address, SPT’s shadow L1 propagation logic erroneously untaints the accessed memory bytes in the L1D, which may contain secret data.

AMuLeT\* misses this likely because our LLVM-IR instrumentation for suppressing architectural faults (like AMuLeT’s) has the unintentional side effect of suppressing most transient faults too. Suppressing architectural faults is needed to prevent our randomly-generated tests from crashing gem5.

To restore security, we upstream and locally apply a patch to SPT that unconditionally taints all output registers at rename [94]. This ensures that the outputs of any transient instructions bypassing the ROB are conservatively tainted, avoiding the above issue, while still allowing SPT to assign the correct taint for instructions that successfully enter the ROB.

| Parameter              | P-core                                | E-core                          |

|------------------------|---------------------------------------|---------------------------------|

| Clock frequency        | 3.4GHz                                | 2.5GHz                          |

| Cores                  | 8 cores                               | 8 cores                         |

| Pipeline width         | 6-way fetch/issue/decode/rename       |                                 |

| ROB/LQ/SQ size         | 512/192/114 entries                   | 256/80/50 entries               |

| Predictors             | 4K-entry BTB, 16-entry RSB, TAGE BP   |                                 |

| Physical register file | 280/332 int/FP regs.                  | 213/207 int/FP regs.            |

| L1D cache (private)    | 48KiB, 12-way                         | 32KiB, 8-way                    |

| L1I cache (private)    | 32KiB, 8-way                          | 64KiB, 8-way                    |

| L2 cache (private)     | 1.25MiB, 10-way                       | 256KiB/2MiB, <sup>†</sup> 8-way |

| L3 cache (shared)      |                                       | 30MiB, 12-way                   |

| Coherence protocol     | Directory-based 3-level MESI protocol |                                 |

TABLE III: Our gem5 processor configuration resembling an Intel Alder Lake hybrid processor. Pipeline parameters (e.g., ROB size) are taken from prior studies [72], [73]. <sup>†</sup>gem5 does not readily support Alder Lake’s mixed private/shared L2 for P-/E-cores, so we model both as private but assign each E-core a 2 MiB L2 for single-threaded workloads and a 256 KiB slice for multi-threaded ones.

Our SPT taint bug fix uncovers a latent performance issue in its implementation: 32-bit register writes (e.g., `mov eax, 42`) implicitly zero the upper 32 bits of the full 64-bit register (e.g., `rax`) but do not untaint them, so subsequent uses of the full register (e.g., `mov [rsp+rax], 0`) are considered tainted, degrading performance. To restore performance, we upstream and locally apply a patch to SPT that untaints the upper 32 bits of a register whenever its lower 32 bits are written to [95].

**Final testing results:** After applying the bug fixes in §VII-B4b and §VII-B4c, AMuLeT\* finds zero contract violations for STT, SPT, and SPT-SB after running 2.7/0.3/1.2 million tests. We evaluate the performance of these fully patched secure baseline implementations in §VIII.

## VIII. PERFORMANCE EVALUATION

In this section, we show that PROTEAN outperforms state-of-the-art comprehensive, programmer-transparent defenses when securing a variety of vulnerable programs.

### A. Experimental Setup

We implement ProtCC as a machine IR pass in LLVM [82].<sup>5</sup> We implement ProtISA and ProtDelay/ProtTrack for the gem5 O3 speculative, out-of-order processor [21].<sup>6</sup> We obtain a performance comparison between PROTEAN and a given baseline on a given benchmark as follows.

*1) Compilation:* First, we use LLVM Clang and Flang 17 [83], [84] to compile each benchmark with and without the appropriate ProtCC pass (§V-A). We refer to the former as the *ProtCC binary* and the latter as the *base binary*. In the special case where the class is non-secret-accessing, the base binary is the ProtCC binary (§V-A1). We similarly compile base and ProtCC versions of LLVM’s libc and libc++ libraries [80], [81] and statically link them with each benchmark as appropriate.

*2) Processor Configuration:* We configure gem5’s O3 CPU to resemble a 12th Gen Intel® Core™ i9-12900KS Alder Lake processor [57], which features a hybrid architecture with 8 Golden Cove performance cores (*P-cores*) and 8 Gracemont efficiency cores (*E-cores*). See Tab. III for details.

<sup>5</sup>ProtCC: <https://github.com/StanfordPLArchSec/protean-llvm>.

<sup>6</sup>PROTEAN gem5: <https://github.com/StanfordPLArchSec/protean-gem5>.

3) *Single-Thread Simulation*: We simulate single-thread workloads on a single P-core or E-core using the SimPoints methodology [121]. We select up to 10 representative 50-million-instruction intervals (*simpoints*) for the base binary. We then use the PinCPU methodology [98] to translate each simpoint for the base binary into the equivalent simpoint of the ProtCC binary that corresponds to the same application region, using source locations as a progress marker. This ensures that we evaluate PROTEAN on the same part of the benchmark as our baselines. We compile both the base and ProtCC binaries with `-O2 -g` to ensure the availability of source locations.

We resume non-PROTEAN baselines from the base binary's simpoints and PROTEAN from the ProtCC binary's translated simpoints. To resume from a simpoint, we warm up each simulated design for 10 million instructions before the instruction interval begins, and then record execution statistics until the instruction interval ends. Finally, we take a weighted sum of each simpoint's simulated execution time to obtain the benchmark's estimated overall execution time.

4) *Multi-Thread Simulation*: We simulate multi-thread benchmarks end-to-end on a full Alder Lake configuration, with 8 P-cores and 8 E-cores (Tab. III).

5) *Evaluated Spectre Defenses*: We evaluate the unmodified O3 CPU (our unsafe baseline) and state-of-the-art comprehensive, programmer-transparent Spectre defenses with hardware-defined ProtSets (our secure baselines)—STT, SPT, and SPT-SB—on base binaries. We omit NDA and SpecShield (§III-C), since STT is more performant [13], [138], [148]. We run all evaluated defenses under the comprehensive AT-COMMIT speculation model (§II-B2), unless otherwise stated.

We evaluate PROTEAN using either its ProtTrack or Prot-Delay protection mechanism, running ProtCC-ARCH/-CTS/-CT/-UNR binaries, for eight total defense configurations. We suffix PROTEAN to denote the protection mechanism in use and which ProtCC pass the binary was compiled with (e.g., PROTEAN-Track-CT for ProtTrack on a ProtCC-CT binary). We omit a protection mechanism (e.g., PROTEAN-CT) to denote both mechanisms paired with the same ProtCC pass (e.g., PROTEAN-Delay-CT and PROTEAN-Track-CT).

We run the rebased implementations of STT, SPT, and SPT-SB described in §VII-B3, with all security and performance fixes described in §VII-B4b and §VII-B4c applied. We evaluate the performance impact of these fixes in §IX-A7.

## B. Experiments

We evaluate PROTEAN on seven general-purpose, single-class, and multi-class benchmark suites.

1) *General-Purpose (SPEC2017, PARSEC)*: To gauge PROTEAN's performance when securing general-purpose code, we evaluate all PROTEAN configurations and all baselines on the single-thread SPEC CPU® 2017 speed (SPEC2017) [24] benchmarks with *reference*-size inputs and the multi-thread PARSEC [20] benchmarks with *simsmall*-size inputs. We omit the `cam4` SPEC2017 benchmark which exceeds a 2-day timeout and `roms` due to a gem5 crash. We omit PARSEC's `bodytrack`, `facesim`, `freqmine`, `raytrace`, `vips`,

| ARCH | STT    | PROTEAN |       | CTS   | SPT    | PROTEAN |       |

|------|--------|---------|-------|-------|--------|---------|-------|

|      |        | Delay   | Track |       |        | Delay   | Track |

| SPEC | P-core | 1.369   | 1.299 | 1.089 | SPEC   | P-core  | 1.708 |

| 2017 | E-core | 1.143   | 1.110 | 1.051 | 2017   | E-core  | 1.302 |

|      | PARSEC | 1.169   | 1.022 | 1.007 | PARSEC |         | 1.409 |

|      |        |         |       |       |        | 1.177   | 1.076 |

| CT   | SPT    | PROTEAN |       | UNR   | SPT-SB | PROTEAN |       |

|      |        | Delay   | Track |       |        | Delay   | Track |

| SPEC | P-core | 1.708   | 1.527 | 1.422 | SPEC   | P-core  | 2.949 |

| 2017 | E-core | 1.302   | 1.212 | 1.176 | 2017   | E-core  | 2.081 |

|      | PARSEC | 1.409   | 1.270 | 1.191 | PARSEC |         | 3.040 |

|      |        |         |       |       |        | 2.125   | 2.088 |

TABLE IV: Geometric mean normalized runtime of all eight of PROTEAN's single-class configurations on SPEC2017 and PARSEC.

`x264`, and `streamcluster` due to gem5 crashes, compile errors, and 5-day timeouts.

2) *Single-Class*: We evaluate PROTEAN on representative single-class workloads to demonstrate that PROTEAN outperforms all state-of-the-art defenses that target each class.

*ARCH-Wasm*: We compare PROTEAN-ARCH to STT on the subset of the SPEC CPU 2006 benchmarks that compile to sandboxed WebAssembly [50], on *reference*-size inputs. We use `wasi-sdk` [136] to compile to WebAssembly, `wasm2c` to transpile it to C, and Clang to compile it to a native executable.

*CTS-Crypto/CT-Crypto*: We compare PROTEAN-CTS/-CT to SPT on cryptographic primitives that are static constant-time (from [97]) and constant-time (from [32]).

*UNR-Crypto*: We compare PROTEAN-UNR to SPT-SB on three OpenSSL cryptographic primitives—modular exponentiation (`ossl.bnexp` in Tab. V), Diffie-Hellman key exchange (`ossl.dh`), and elliptic curve addition (`ossl.ecadd`)—that are *not* constant-time (curated by us).

3) *Multi-Class (NGINX)*: To showcase how ProtCC enables PROTEAN to performantly secure complex multi-class applications, we compare PROTEAN to SPT-SB on the nginx HTTPS web server [100], which mixes all four classes (Fig. 1). The main nginx executable does not access secrets, so we compile it with ProtCC-ARCH (§V-A1). Instead, it delegates secret computation to OpenSSL [104], which contains all classes of code (including non-constant-time, §III-A). We compile OpenSSL with ProtCC-UNR for security, except for the 2/7/1 hottest ARCH/CTS/CT functions, which we identify via runtime profiling, classify manually by examining the source, and compile with ProtCC-ARCH/-CTS/-CT for performance. Like prior work [118], we use `siege` [124], running directly on the host, to connect a variable number of clients  $c$ , each issuing a varying number of requests  $r$ , to the gem5-simulated server.

## IX. PERFORMANCE RESULTS

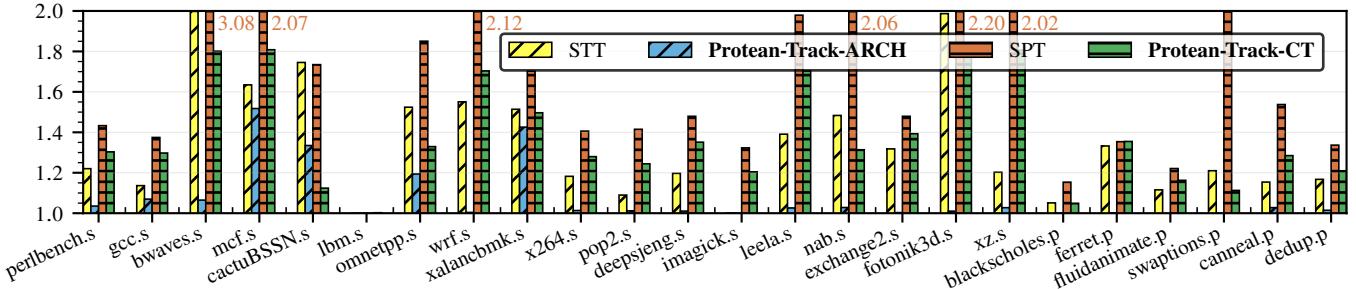

Fig. 6, Tab. IV, and Tab. V present the results to the experiments described in §VIII.

### A. General-Purpose Workloads (Fig. 6, Tab. IV)

Fig. 6 plots per-benchmark normalized runtimes for PROTEAN-Track-ARCH/-CT and STT/SPT on SPEC2017 (on a P-core) and PARSEC. Tab. IV reports the geomean normalized runtimes for all defenses and core types. On a P-core, PROTEAN-Track-ARCH/-CT averages less than one-fourth/two-

Fig. 6: Normalized runtime of PROTEAN-Track-ARCH/-CT versus STT/SPT on the SPEC2017 benchmarks (\*.s) on a P-core and PARSEC (\*.p) benchmarks on the full Alder Lake configuration.

| ARCH-Wasm       | STT   | PROTEAN |       | CT-Crypto              | SPT   | PROTEAN |       |

|-----------------|-------|---------|-------|------------------------|-------|---------|-------|

|                 |       | Delay   | Track |                        |       | Delay   | Track |

| bzip2           | 2.771 | 1.201   | 1.110 | bearssl                | 1.444 | 1.278   | 1.265 |

| mcf             | 3.270 | 1.429   | 1.333 | ctaes                  | 1.372 | 1.129   | 1.006 |

| milc            | 3.729 | 1.212   | 1.017 | djbsort                | 1.264 | 1.256   | 1.238 |

| namd            | 2.860 | 1.042   | 1.006 | geomean                | 1.358 | 1.219   | 1.163 |

| libquantum      | 2.002 | 1.344   | 1.003 | UNR-Crypto             |       | SPT-SB  |       |

| lmb             | 1.364 | 1.001   | 1.001 | PROTEAN                |       | PROTEAN |       |

| geomean         | 2.533 | 1.195   | 1.072 | ossi.bnexp             | 2.590 | 2.628   | 2.624 |

| CTS-Crypto      | SPT   | PROTEAN |       | ossi.dh                | 3.137 | 2.566   | 2.548 |

|                 |       | Delay   | Track | ossi.ecadd             | 2.897 | 2.916   | 2.913 |

| hacl.chacha20   | 1.008 | 1.068   | 0.999 | geomean                | 2.866 | 2.699   | 2.690 |

| hacl.curve25519 | 1.026 | 1.071   | 0.991 | Multi-Class Web Server |       | SPT-SB  |       |

| hacl.poly1305   | 1.158 | 1.000   | 1.001 | nginx.c1r1             | 2.746 | 1.569   | 1.408 |

| sodium.salsa20  | 1.000 | 1.115   | 1.115 | nginx.c2r2             | 2.776 | 1.469   | 1.310 |

| sodium.sha256   | 1.174 | 1.073   | 1.073 | nginx.c1r4             | 2.778 | 1.472   | 1.311 |

| ossi.chacha20   | 1.096 | 1.002   | 1.002 | nginx.c4r1             | 2.775 | 1.473   | 1.311 |

| ossi.curve25519 | 1.109 | 1.118   | 1.101 | nginx.c4r4             | 2.787 | 1.428   | 1.267 |

| ossi.sha256     | 1.367 | 1.062   | 1.061 | geomean                | 2.772 | 1.481   | 1.321 |

| geomean         | 1.112 | 1.063   | 1.042 |                        |       |         |       |